新書推薦:

《

中国摄影 中式摄影的独特魅力

》

售價:HK$

1097.6

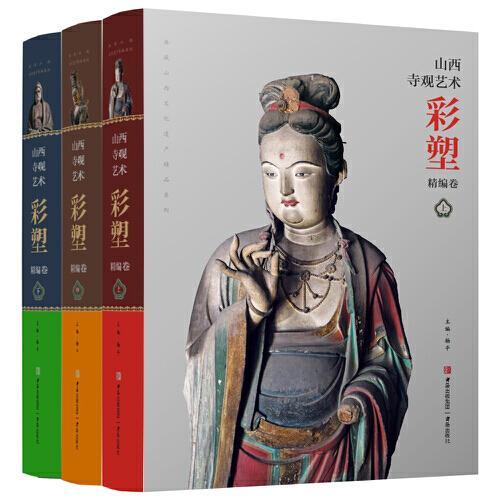

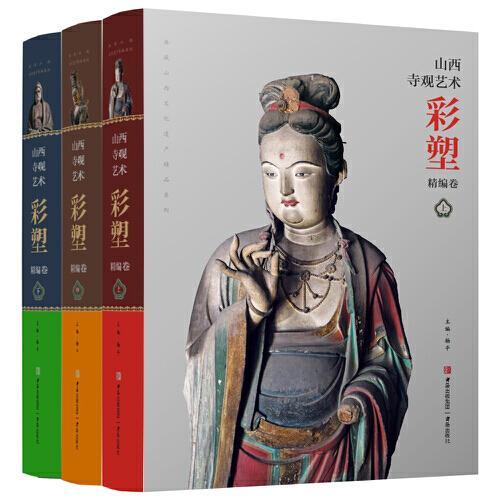

《

山西寺观艺术彩塑精编卷

》

售價:HK$

1680.0

《

积极心理学

》

售價:HK$

55.8

《

自由,不是放纵

》

售價:HK$

54.9

《

甲骨文丛书·消逝的光明:欧洲国际史,1919—1933年(套装全2册)

》

售價:HK$

277.8

《

剑桥日本戏剧史(剑桥世界戏剧史译丛)

》

售價:HK$

201.6

《

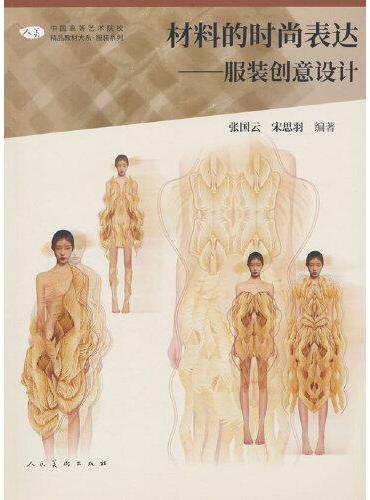

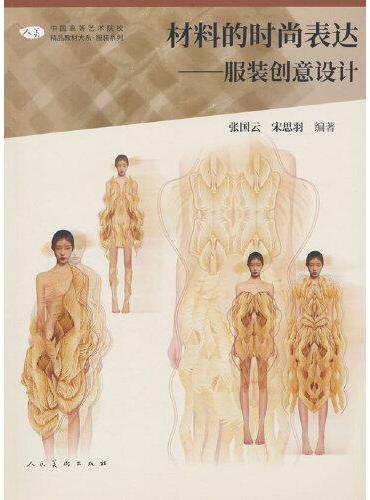

中国高等艺术院校精品教材大系:材料的时尚表达??服装创意设计

》

售價:HK$

76.2

《

美丽与哀愁:第一次世界大战个人史

》

售價:HK$

143.4

|

| 內容簡介: |

魏欣、顾斌、姜志鹏主编的《数字电路EDA设计 第3版普通高等教育十一五***规划教材》以提高 高校学生的数字电子系统工程设计能力为宗旨,对 EDA技术基本知识、可编程逻辑器件的原理、硬件描 述语言及其编程方法和数字电路EDA设计方法作了系 统介绍。本书的特点是语言精练,实例丰富,深入浅 出,注重实用,适合广大高职院校学生的特点和教学 改革方向。

全书共分6章,**章为绪论,介绍EDA技术的基 本知识;第2章以国内市场占有率*高的两类芯片, 即Altera公司和Xilinx公司的典型芯片为例,介绍了 CPLD与FPGA的基本原理;第3章介绍数字电路:EDA开 发工具,包含目前业界常用的工具软件ModelSim与 Quartus II的使用,以及二者联合使用的方法;第4 章介绍了VHDL基本语法,并以具体实例解析VHDL的编 程思想;第5章介绍基本数字电路的EDA实现方法,从 语言编程、软件仿真、硬件验证三大步骤,对各类基 本逻辑电路的EDA实现方法作了详细的阐述;第6章是 典型数字系统设计,通过丰富实用的典型案例介绍多 种数字系统的设计方法。

本书可作为高等职业院校电子类、通信类、电气 类、计算机技术类等工科专业学生的数字逻辑电路、 VHDL程序设计、EDA技术等相关课程的教材或相应实 验课程的指导书,也可供从事数字电子系统设计的专 业技术人员参考。

|

| 目錄:

|

第1章 绪论

1.1 概述

1.2 EDA技术的应用领域

1.3 EDA的设计步骤

1.4 TOP-DOWN设计方法

1.5 硬件描述语言

1.5.1 ABEL-HDL

1.5.2 Verilog-HDL

1.5.3 VHDL

1.5.4 Verilog-HDL和VHDL的比较

1.6 可编程逻辑器件开发工具

1.6.1 ispLEVER

1.6.2 ISE

1.6.3 QuarmsII

1.7 IP核概述

第2章 CPLD、FPGA芯片结构

2.1 Altera公司CPLD芯片

2.1.1 概述

2.1.2 功能描述

2.1.3 逻辑阵列块

2.1.4 用户Flash存储区

2.2 Xilinx公司Virtex-5系列FPGA

2.2.1 概述

2.2.2 可配置逻辑块CLB

2.2.3 输入输出模块IOB

2.2.4 BlockRAM

习题

第3章 数字电路EDA开发工具

3.1 ModelSim的设计过程

3.1.1 新建工程与源文件

3.1.2 ModelSim仿真

3.2 QuartusII的设计过程

3.2.1 设计输入

3.2.2 编译

3.2.3 编译前的约束设置

3.2.4 仿真前的参数设置

3.2.5 仿真

3.2.6 引脚分配

3.3 QuartusII与ModelSim联合仿真

3.3.1 存储器初始化文件

3.3.2 MegaWizardPlus-InManager定制ROM

3.3.3 QuartusII与ModelSim联合仿真

3.4 ISEDesignSuite集成开发环境

3.4.1 ISEDesignSuite各功能模块简介

3.4.2 ISEFoundation软件介绍

3.5 ISEFoundation设计流程

3.5.1 问题分析

3.5.2 设计输入

3.5.3 工程编译

3.5.4 仿真验证

3.5.5 器件配置与编程

习题

第4章 VHDL语言

4.1 VHDL概述

4.1.1 VHDL的特点

4.1.2 VHDL语言的程序结构

4.1.3 VHDL程序的一般结构

4.2 实体定义相关语句

4.2.1 类属参数说明语句

4.2.2 端口说明语句

4.3 结构体及子结构语句

4.3.1 结构体的格式及构造

4.3.2 子结构之块(BLOCK)语句结构

4.3.3 子结构之进程(PROCESS)语句结构

4.3.4 子结构之子程序FUNCTION语句结构

4.3.5 子结构之子程序PROCEDURE语句结构

4.4 程序包、库及配置

4.4.1 程序包

4.4.2 库

4.4.3 配置

4.5 VHDL的并行语句

4.5.1 简单信号赋值语句

4.5.2 选择信号赋值语句

4.5.3 条件信号赋值语句

4.5.4 元件例化语句

4.5.5 生成语句

4.6 VHDL中的顺序语句

4.6.1 顺序赋值语句

4.6.2 IF语句

4.6.3 CASE语句

4.6.4 WAIT语句

4.6.5 LOOP语句

4.7 VHDL语言的客体及其分类

4.7.1 常数

4.7.2 变量

4.7.3 信号

4.8 VHDL语言的标准数据类型

4.8.1 位

4.8.2 位矢量

4.8.3 布尔量

4.8.4 整数

4.8.5 实数

4.8.6 字符

4.8.7 字符串

4.8.8 时间

4.8.9 错误等级

4.9 VHDL用户定义的数据类型

4.9.1 枚举类型

4.9.2 整数类型

4.9.3 数组

4.9.4 用户自定义子类型

4.10 VHDL语言的运算操作符

4.10.1 逻辑运算符

4.10.2 算术运算符

4.10.3 关系运算符

习题

第5章 基本数字电路的EDA实现

5.1 基本门电路的设计

5.2 触发器的设计

5.3 编码器的设计

5.3.1 BCD编码器

5.3.2 格雷码编码器

5.4 译码器的设计

5.4.1 二进制译码器

5.4.2 数码显示译码器

5.5 计数器的设计

5.5.1 带使能、清零、预置功能的计数器

5.5.2 可逆计数器

5.5.3 进制计数器

5.6 移位寄存器的设计

5.6.1 串入串出移位寄存器

5.6.2 同步预置串行输出移位寄存器

5.6.3 循环移位寄存器

5.6.4 双向移位寄存器

5.7 有限状态机的设计

5.7.1 莫尔型状态机

5.7.2 米里型状态机

5.7.3 QuartusII观察状态转换图

习题

第6章 典型数字系统设计

6.1 分频电路

6.1.1 偶数分频

6.1.2 奇数分频

6.1.3 X.5分频

6.1.4 6.5分频器的硬件验证

6.2 交通灯控制器

6.2.1 交通灯控制器的功能描述

6.2.2 交通灯控制器的实现

6.2.3 交通灯控制器的VHDL程序

6.2.4 交通灯控制器的硬件验证

6.3 数字频率计

6.3.1 测频原理

6.3.2 频率计的组成结构分析

6.3.3 频率计的VHDL程序

6.3.4 频率计的仿真结果

6.3.5 频率计的硬件验证

6.4 实用数字钟电路

6.4.1 分频模块

6.4.2 时钟产生模块

6.4.3 数码管显示驱动模块

6.4.4 数字钟的硬件验证

6.5 LCD接口控制电路

6.5.1 1602字符LCM的内部存储器

6.5.2 1602字符LCM的引脚

6.5.3 1602LCM指令系统

6.5.4 1602LCM控制过程

6.5.5 1602显示的硬件验证

6.6 串口通信

6.6.1 异步串口数据传送格式

6.6.2 用VHDL描述RS-232C串口

6.6.3 串口通信的VHDL程序仿真结果

6.6.4 串口通信的硬件验证

6.7 2FSK信号产生器

6.7.1 FSK基本原理

6.7.2 2FSK信号产生器

6.7.3 2FSK信号产生器的VHDL描述

6.7.4 2FSK的仿真结果

6.7.5 2FSK的硬件验证

习题

附录一 实验电路板结构图

附录二 实验板电气原理图

附录三 实验板EPM240管脚定义表

参考文献

|

|